One for the analogue experts:

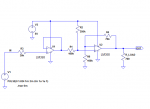

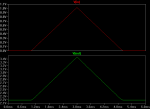

I want to produce a voltage between 2.2 and 3.5 volts with around 5ma drive capability from the DAC on a 08M2. I'm using the internal voltage reference FVR4096 as the +ve input to the DAC

If I just put the DAC output into a rail-to-rail opamp (MCP612). Then I can only use 11 levels (15-25). I need around double this for the application.

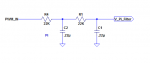

So I need to scale the DAC output by a factor of 1.3/4.096 and add a 2.2V bias voltage. I tried 75K:18K resistor divider on the input to the opamp, in theory to limit the voltage to around 3.5V, but even that 93Kohm load killed the DAC output.

Help appreciated

Thanks

Peter

I want to produce a voltage between 2.2 and 3.5 volts with around 5ma drive capability from the DAC on a 08M2. I'm using the internal voltage reference FVR4096 as the +ve input to the DAC

If I just put the DAC output into a rail-to-rail opamp (MCP612). Then I can only use 11 levels (15-25). I need around double this for the application.

So I need to scale the DAC output by a factor of 1.3/4.096 and add a 2.2V bias voltage. I tried 75K:18K resistor divider on the input to the opamp, in theory to limit the voltage to around 3.5V, but even that 93Kohm load killed the DAC output.

Help appreciated

Thanks

Peter