kranenborg

Senior Member

Hello Rodney and other interested forum members,

Here is information on the beta test versions of SerialPower II, now with test codes for both M2 and X2 (a system may combine them both).

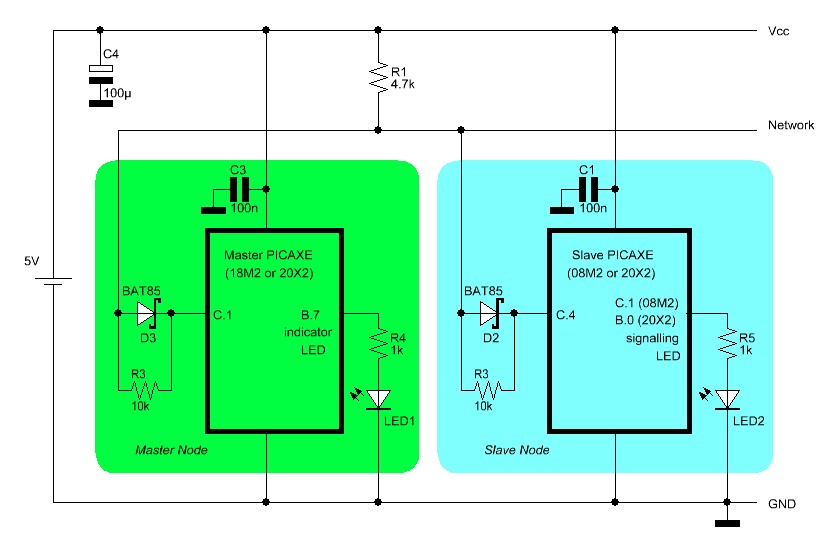

The test system that I propose (and have used succesfully with the M2 picaxes) is as follows:

The only change that I made regarding to the previous setup was to have the network input / output pin identical, which saves particularly on a 08M2

Here follow the test codes for M2 and X2 respectively all appliccable to the above circuit. The M2 codes function perfectly at my prototype, but I do not have any X2 to test so I would appreciate if people who do possess one or more X2 processors could test the X2 codes as well:

M2 master and slave codes (here for 18M2 master and 08M2 slave):

http://www.kranenborg.org/ee/picaxe/SerialPower/II/M2/II_BETA_M2_MASTER_18M2.BAS

http://www.kranenborg.org/ee/picaxe/SerialPower/II/M2/II_BETA_M2_SLAVE_08M2.BAS

X2 master and slave codes (here for 20X2 master and 20X2 slave):

http://www.kranenborg.org/ee/picaxe/SerialPower/II/X2/II_BETA_X2_MASTER_20X2.BAS

http://www.kranenborg.org/ee/picaxe/SerialPower/II/X2/II_BETA_X2_SLAVE_20X2.BAS

The codes can be used for other M2 and X2 variants as well as for different input/output pins. In the latter case, a change of input pin should also be reflected in the interrupt mask! The X1 variants could not be implemented since these do not have the required bidirectional flexibility for serial operations.

I would be really thankful if those who test could report their outcome here.

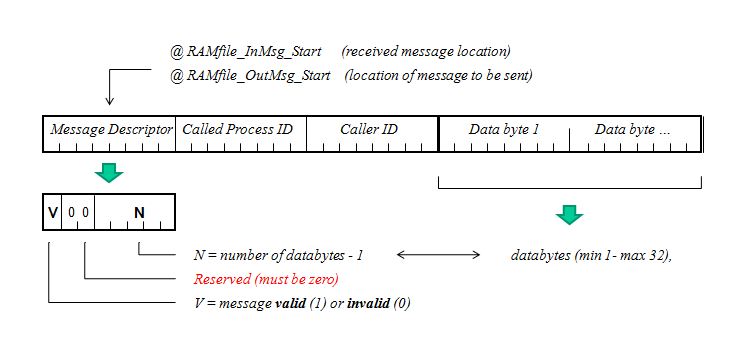

Note that there are some slight code differences between the M2 and X2 variants, all because of the fact that the RAM areas for getting and storing messages are different; the X2 variants use the scratchpad area whilst the M2 use regular RAM. This means in practice that when accessing the RAM message areas the following conditions hold:

- M2: use PEEK and POKE to access the message RAM areas and use the bptr pointer where relevant

- X2: use GET and PUT to access the message RAM areas and use the ptr pointer where relevant

The differences become clear when comparing files with a tool like WinMerge etc.

The output to be expected is described in item #37 but repeated here for completeness:

Thanks, and let me know your experiences!

/Jurjen

http://www.kranenborg.org/electronics

Here is information on the beta test versions of SerialPower II, now with test codes for both M2 and X2 (a system may combine them both).

The test system that I propose (and have used succesfully with the M2 picaxes) is as follows:

The only change that I made regarding to the previous setup was to have the network input / output pin identical, which saves particularly on a 08M2

Here follow the test codes for M2 and X2 respectively all appliccable to the above circuit. The M2 codes function perfectly at my prototype, but I do not have any X2 to test so I would appreciate if people who do possess one or more X2 processors could test the X2 codes as well:

M2 master and slave codes (here for 18M2 master and 08M2 slave):

http://www.kranenborg.org/ee/picaxe/SerialPower/II/M2/II_BETA_M2_MASTER_18M2.BAS

http://www.kranenborg.org/ee/picaxe/SerialPower/II/M2/II_BETA_M2_SLAVE_08M2.BAS

X2 master and slave codes (here for 20X2 master and 20X2 slave):

http://www.kranenborg.org/ee/picaxe/SerialPower/II/X2/II_BETA_X2_MASTER_20X2.BAS

http://www.kranenborg.org/ee/picaxe/SerialPower/II/X2/II_BETA_X2_SLAVE_20X2.BAS

The codes can be used for other M2 and X2 variants as well as for different input/output pins. In the latter case, a change of input pin should also be reflected in the interrupt mask! The X1 variants could not be implemented since these do not have the required bidirectional flexibility for serial operations.

I would be really thankful if those who test could report their outcome here.

Note that there are some slight code differences between the M2 and X2 variants, all because of the fact that the RAM areas for getting and storing messages are different; the X2 variants use the scratchpad area whilst the M2 use regular RAM. This means in practice that when accessing the RAM message areas the following conditions hold:

- M2: use PEEK and POKE to access the message RAM areas and use the bptr pointer where relevant

- X2: use GET and PUT to access the message RAM areas and use the ptr pointer where relevant

The differences become clear when comparing files with a tool like WinMerge etc.

The output to be expected is described in item #37 but repeated here for completeness:

Thanks, and let me know your experiences!

/Jurjen

http://www.kranenborg.org/electronics

Last edited: