I am attempting to receive a 2-byte sequence using an 08M2+ at 2400 baud via HSERIN on C.1 (pin 6). The code loops, reading HSERIN until a qualified 1st byte is received. The code then moves on to read the 2nd byte approx 10 mSec later. At 2400 baud the byte is sent in approx 4.2 mSec (10 bits).

The problem I'm observing is that the 2nd byte is not always read correctly. If both bytes are read after they both have been received then the data is good. If the 1st byte is read before the 2nd byte is sent then that's OK as well.

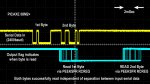

The problem occurs when the 1st byte is read while the 2nd byte is being received. The corrupted 2nd byte is read as either 1) the 1st byte, 2) $FF or 3) part of the 2nd byte shifted over by a nibble ($F4). The correct 2nd byte has the value $46.

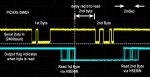

I have changed the timing of how data is both sent and received and observed the waveforms on a scope while outputting the data received by the 08M2+ to a terminal.

The results are very repeatable in terms of when the 2nd byte is corrupted. This bad data zone occurs when the reading of the 1st byte occurs after the 1st data bit of the 2nd byte and approximately two bit times after the 2nd byte's stop bit.

Has any one else seen this problem?

The problem I'm observing is that the 2nd byte is not always read correctly. If both bytes are read after they both have been received then the data is good. If the 1st byte is read before the 2nd byte is sent then that's OK as well.

The problem occurs when the 1st byte is read while the 2nd byte is being received. The corrupted 2nd byte is read as either 1) the 1st byte, 2) $FF or 3) part of the 2nd byte shifted over by a nibble ($F4). The correct 2nd byte has the value $46.

I have changed the timing of how data is both sent and received and observed the waveforms on a scope while outputting the data received by the 08M2+ to a terminal.

The results are very repeatable in terms of when the 2nd byte is corrupted. This bad data zone occurs when the reading of the 1st byte occurs after the 1st data bit of the 2nd byte and approximately two bit times after the 2nd byte's stop bit.

Has any one else seen this problem?