Resolving Serin & Serout Errors on 20X2 and 20M2 Picaxe Chips

This note only deals with the Picaxe 20X2 and 20M2. However other Picaxe chips may have similar issues and should be tested.

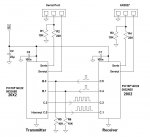

In the process of working on a project that used both a 20X2 and a 20M2, I tried to send 2 bytes of serial data from the 20X2 to the 20M2 at 9600 baud using software serout and serin. No matter what I did not single byte could be received without error.

Both Picaxe Chips were set to 8Mhz. The 20X2 used " serout C.0, N9600_8, ($55,$55)" and the 20M2 used "serin c.0, n9600_8, b0,b1". A qualifier was added as well as delays but to no avail. The baud was reduced to 4800 but still no good. Only at 2400 baud was data able to be sent & received.

So I got out my newly acquired TEK THS730A digital scope and started testing. Here is what I found.

20X2

The Fix ? ... There is none....at least not at 9600_8 and other some other settings. Calibfreq has to be taken all the way to 31 on the 20x2 and to -15 on the M2 to get a single byte through. And at these settings sertxd fails with corrupted data to the PE terminal, not to mention the adverse affects on pulsout & pwm timings.

The good news is that the serout error on the 20X2 is less than 1 percent at 9600_16 with an actual baud rate of 9557. The serin error on the 20M2 is less than 1 percent at 9600_16 with an actual center baud rate of 9690... Both really good for software (bit- banged serial). And at this setting for both chips, unlimited back to back bytes can be sent & received without error.

By doing extensive testing on both chips severe accuracy problems were found at certain settings on each.At other settings the accuracy is good.

To keep this from being too boring, attached is a chart of the of the actual baud rates of serout and serin in for all possible frequency / baud combinations of these two Picaxe Chips from 2400 to 38400 baud and from 4Mhz to 32Mhz.

Solutions? ... All are work arounds .

1. Refer to the attached tables and use frequency / baud combinations that have the least error or that are compatible even with the error.

For example, a 20M2 can send and receive data to another 20M2 at 9600_8 because the error for both serin and serout is in the same direction. However, a 20X2 at 4800_4 cannot send data to a 20M2 at 4800_4 because the actual serout baud rate of the 20X2 is outside of the serin range of the 20M2.

2. If you must use a certain baud rate at a certain frequency/ baud combination that shows the 4% error or 6.1% serin error ( 9600_8 is very common), use hardware hserout instead of "serout" . This would be particularly applicable for serout 9600_8 with the 20X2 at 8mhz. 9158 baud is so far out of specification that it will likely fail with most any other device, even another 20X2.

What won't work.

1. Using a qualifier if the serout baud rate is outside of the "range" of the serin rate. The qualifier cannot be recognized reliably.

2. Adding a delay between bytes sent when serout is outside of the range of serin. Delays will not solve gross accuracy problems.

It is a myth that serin cannot process back to back bytes fast enough at 8mhz and above. Pacing, was only an issue in my testing at 2400_4 where the processor overhead is the highest and when the space between bytes was less than 900us. This can be easily proven at 8 Mhz and above by sending 32 back to back bytes at a rate within the serin expected range, (without a qualifier) . It works fine.

Attached are tables that show the actual baud rates for every serin / serout setting on the 20X2 & 202M2 chips from 2400 to 38400 baud. 64mhz was not tested on the 20X2.

EDIT:

The tables have shaded rows that indicate serial baud / processor frequency combinations that should be avoided.

It should be noted that a 20M2 CAN communicate with another 20M2 at these high error settings because the error for both serin and serout is in the same direction.

However a 20X2 cannot communicate with another 20X2 at these settings because the baud rate error for serin and serout is in opposite directions.

This note only deals with the Picaxe 20X2 and 20M2. However other Picaxe chips may have similar issues and should be tested.

In the process of working on a project that used both a 20X2 and a 20M2, I tried to send 2 bytes of serial data from the 20X2 to the 20M2 at 9600 baud using software serout and serin. No matter what I did not single byte could be received without error.

Both Picaxe Chips were set to 8Mhz. The 20X2 used " serout C.0, N9600_8, ($55,$55)" and the 20M2 used "serin c.0, n9600_8, b0,b1". A qualifier was added as well as delays but to no avail. The baud was reduced to 4800 but still no good. Only at 2400 baud was data able to be sent & received.

So I got out my newly acquired TEK THS730A digital scope and started testing. Here is what I found.

20X2

- When set to 9600_8 the actual serout baud rate is 9158. This is a -4% error.

- When set to receive with serin 9600_8, data can be reliably received only between 9808 and 10570, meaning serin 9600_8 is set by firmware to receive at a center baud rate of 10189. This is an error of 6.1% from a nominal 9600.

- When set to 9600_8 the actual serout baud rate is 9882. This is an error of +3.0%

- When set to receive with serin 9600_8, data can be reliably received only between 9624 and 10650, meaning serin 9600_8 is set by firmware to receive at a center baud rate of 10137. This is 6% error.

The Fix ? ... There is none....at least not at 9600_8 and other some other settings. Calibfreq has to be taken all the way to 31 on the 20x2 and to -15 on the M2 to get a single byte through. And at these settings sertxd fails with corrupted data to the PE terminal, not to mention the adverse affects on pulsout & pwm timings.

The good news is that the serout error on the 20X2 is less than 1 percent at 9600_16 with an actual baud rate of 9557. The serin error on the 20M2 is less than 1 percent at 9600_16 with an actual center baud rate of 9690... Both really good for software (bit- banged serial). And at this setting for both chips, unlimited back to back bytes can be sent & received without error.

By doing extensive testing on both chips severe accuracy problems were found at certain settings on each.At other settings the accuracy is good.

To keep this from being too boring, attached is a chart of the of the actual baud rates of serout and serin in for all possible frequency / baud combinations of these two Picaxe Chips from 2400 to 38400 baud and from 4Mhz to 32Mhz.

Solutions? ... All are work arounds .

1. Refer to the attached tables and use frequency / baud combinations that have the least error or that are compatible even with the error.

For example, a 20M2 can send and receive data to another 20M2 at 9600_8 because the error for both serin and serout is in the same direction. However, a 20X2 at 4800_4 cannot send data to a 20M2 at 4800_4 because the actual serout baud rate of the 20X2 is outside of the serin range of the 20M2.

2. If you must use a certain baud rate at a certain frequency/ baud combination that shows the 4% error or 6.1% serin error ( 9600_8 is very common), use hardware hserout instead of "serout" . This would be particularly applicable for serout 9600_8 with the 20X2 at 8mhz. 9158 baud is so far out of specification that it will likely fail with most any other device, even another 20X2.

What won't work.

1. Using a qualifier if the serout baud rate is outside of the "range" of the serin rate. The qualifier cannot be recognized reliably.

2. Adding a delay between bytes sent when serout is outside of the range of serin. Delays will not solve gross accuracy problems.

It is a myth that serin cannot process back to back bytes fast enough at 8mhz and above. Pacing, was only an issue in my testing at 2400_4 where the processor overhead is the highest and when the space between bytes was less than 900us. This can be easily proven at 8 Mhz and above by sending 32 back to back bytes at a rate within the serin expected range, (without a qualifier) . It works fine.

Attached are tables that show the actual baud rates for every serin / serout setting on the 20X2 & 202M2 chips from 2400 to 38400 baud. 64mhz was not tested on the 20X2.

EDIT:

The tables have shaded rows that indicate serial baud / processor frequency combinations that should be avoided.

It should be noted that a 20M2 CAN communicate with another 20M2 at these high error settings because the error for both serin and serout is in the same direction.

However a 20X2 cannot communicate with another 20X2 at these settings because the baud rate error for serin and serout is in opposite directions.

Attachments

-

196.1 KB Views: 367

Last edited: